Desde que os primeiros rumores surgiram no início de 2021, a tecnologia de empilhamento de memória da AMD tem vindo a redefinir o desempenho no mundo dos processadores, especialmente no que toca ao gaming. O conceito, que se materializou na famosa 3D V-Cache, consiste essencialmente no empilhamento vertical da cache de último nível (LLC), permitindo aumentar drasticamente a capacidade num espaço físico reduzido.

Atualmente na sua segunda geração, esta tecnologia provou ser um trunfo valioso para a gigante dos semicondutores. Um exemplo recente deste sucesso foi o lançamento, durante a CES 2026, do Ryzen 7 9850X3D, que chegou ao mercado com a audaz reivindicação de ser o processador de jogos mais rápido do mundo. No entanto, a empresa não parece estar satisfeita em ficar apenas pela cache de nível 3 (L3) e já está a explorar novas formas de otimizar a sua hierarquia de memória.

Do L3 para o L2: A procura por menor latência

Na arquitetura Zen, a cache que habitualmente recebe o tratamento 3D é a L3. Contudo, um novo registo de propriedade intelectual sugere que a fabricante está a preparar-se para aplicar uma lógica semelhante à cache de nível 2 (L2), com o objetivo de obter ganhos ainda maiores em desempenho e eficiência energética.

De acordo com o registo da patente, a AMD denomina este novo design de “Balanced Latency Stacked Cache” (Cache Empilhada de Latência Equilibrada). O objetivo primordial é reduzir os atrasos no acesso à memória e melhorar a eficiência energética nos futuros processadores Ryzen X3D.

Comparativamente aos processadores com cache 3D, os modelos convencionais com cache planar sofrem de latências mais elevadas e custos energéticos superiores, o que se traduz numa menor eficiência. Com este novo design de memória cache L2 em 3D, a empresa afirma conseguir reduzir o número de ciclos necessários para aceder a uma cache L2 típica de 1 MB. A melhoria seria de 14 ciclos para apenas 12 ciclos.

Embora uma redução de dois ciclos possa parecer irrelevante para o utilizador comum, no design de arquitetura de CPU, onde cada nanossegundo conta, esta otimização é motivo de entusiasmo. Considerando que uma cache L2 típica opera num intervalo de 10 a 50 ciclos, conseguir "limar" estas arestas pode resultar num impacto significativo na performance final.

Como funciona a estrutura equilibrada

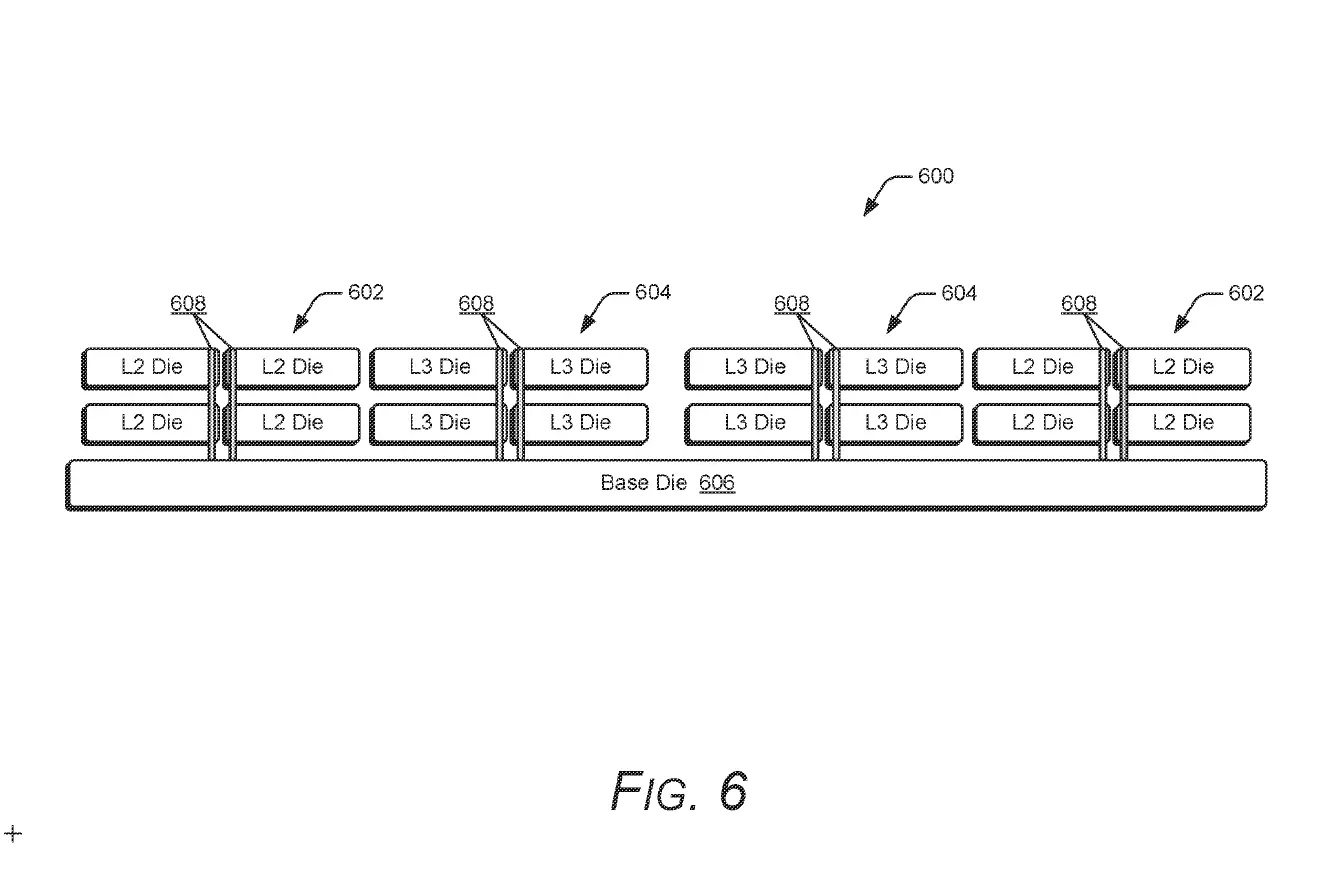

Para tornar isto possível, o documento técnico explica que os "dies" empilhados são ligados através de vias de conexão, como as TSVs (Through-Silicon Vias) ou BPVs (Bond Pad Vias), permitindo a comunicação vertical entre as camadas de silício. O segredo deste design reside no encaminhamento destas conexões através do centro da estrutura.

Ao centralizar as vias de conexão, a AMD consegue encurtar o comprimento dos fios e os estágios de comunicação. Além disso, esta abordagem cria uma estrutura simétrica ou "equilibrada", o que ajuda a garantir que os tempos de acesso aos dados sejam uniformes em todas as camadas. É precisamente esta característica que dá nome à patente.

Como acontece com qualquer registo de patente, é importante notar que a existência do documento não garante que a tecnologia chegue imediatamente ao mercado ou que seja implementada exatamente desta forma. Existe frequentemente uma distância considerável entre a expectativa teórica e o desempenho no mundo real, mas este passo indica claramente que a inovação no empilhamento de chips está longe de terminar.

Nenhum comentário

Seja o primeiro!