A crescente complexidade da Inteligência Artificial (IA) e da computação de alto desempenho (HPC) está a exigir processadores cada vez mais potentes e com maior largura de banda de memória. Para responder a esta necessidade, os designs multi-chiplet já são uma realidade nos processadores de topo atuais, especialmente os que alimentam centros de dados e cargas de trabalho de IA.

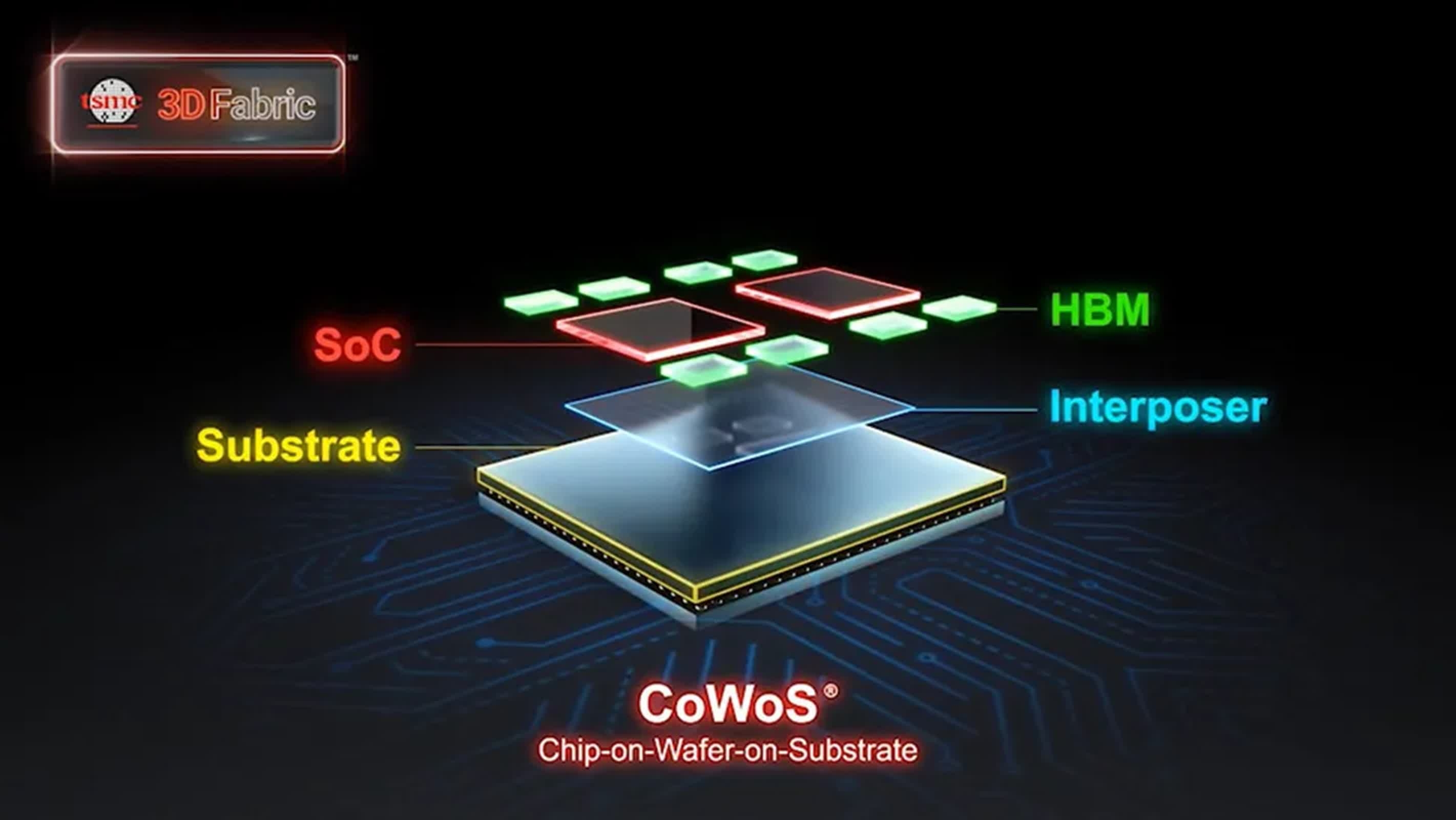

Atualmente, a TSMC, líder na fabricação de semicondutores, utiliza a sua tecnologia CoWoS (Chip-on-Wafer-on-Substrate) que permite acomodar interposers (a camada de ligação entre os chiplets e o substrato) com áreas até 2.831 mm2, mais de três vezes o tamanho de uma máscara fotográfica padrão (limitada a 830-858 mm² pela litografia EUV). Exemplos desta tecnologia em ação incluem os GPUs Instinct MI300X da AMD e B200 da Nvidia, que combinam grandes conjuntos de chiplets de computação com memória de alta largura de banda (HBM).

A Evolução para Embalagens Maiores: CoWoS-L

Contudo, o apetite por mais silício não pára de crescer. Para enfrentar este desafio, a TSMC está a desenvolver uma nova tecnologia de encapsulamento, a CoWoS-L, com lançamento previsto já para o próximo ano. Esta inovação suportará interposers gigantescos de até 4.719 mm² (cerca de 5,5 vezes o limite da máscara) e exigirá substratos de 100x100 mm. Esta área permitirá integrar até 12 stacks de memória HBM, um salto significativo face às capacidades atuais.

A TSMC projeta que os chips construídos com esta tecnologia oferecerão mais de 3,5 vezes o desempenho computacional dos designs líderes de hoje, preparando o terreno para futuros processadores como os GPUs Rubin da Nvidia.

O Futuro: Dimensões Sem Precedentes

Olhando mais à frente, a TSMC planeia ir ainda mais longe com uma embalagem de 7.885 mm² montada num substrato de 120x150 mm – uma área ligeiramente maior que uma caixa de CD padrão. Isto representa um aumento de 9,5 vezes sobre o limite da máscara e quase duplica a área da sua embalagem anterior de 8x.

Uma montagem tão massiva poderia albergar quatro sistemas empilhados em 3D (SoICs - Systems-on-Integrated-Chips), doze stacks de memória HBM4 e múltiplos dies de entrada/saída (I/O), estabelecendo um novo padrão de desempenho e integração.

Para os clientes com as necessidades de desempenho mais extremas, a TSMC oferece também a sua tecnologia System-on-Wafer (SoW-X), que permite a integração de wafers inteiros num único "chip". Embora atualmente poucas empresas utilizem esta abordagem (como a Cerebras e a Tesla para processadores de IA especializados), a TSMC antecipa uma adoção mais ampla à medida que a procura por chips de grande escala aumenta.

Os Desafios da Engenharia: Energia, Tamanho e Calor

Construir estes processadores colossais acarreta desafios de engenharia consideráveis.

Fornecimento de Energia: Grandes conjuntos multi-chiplet podem consumir quilowatts de energia, muito além do que os designs de servidores tradicionais conseguem fornecer. Para resolver isto, a TSMC está a integrar circuitos avançados de gestão de energia diretamente na embalagem do chip. Utilizando a sua tecnologia FinFET N16, a empresa incorpora ICs monolíticos de gestão de energia e indutores no wafer diretamente no substrato CoWoS-L. Esta abordagem permite encaminhar a energia de forma eficiente através da embalagem, reduzindo a resistência elétrica, melhorando a integridade da energia e permitindo o escalonamento dinâmico da tensão para responder rapidamente às mudanças na carga de trabalho. Condensadores deep trench embebidos ajudam a estabilizar o desempenho elétrico. Isto reflete uma mudança para a co-otimização ao nível do sistema, onde energia, encapsulamento e design de silício são tratados como elementos interligados.

Dimensões Físicas: O tamanho físico dos novos substratos (100x100 mm e 120x150 mm) está a levar ao limite os padrões de módulos existentes, como o OAM 2.0, e pode exigir novas abordagens no design de sistemas e placas.

Gestão Térmica: À medida que os processadores crescem em tamanho e consumo, geram enormes quantidades de calor. Os fabricantes de hardware estão a explorar técnicas avançadas de arrefecimento, incluindo arrefecimento líquido direto e por imersão. A TSMC já colaborou com parceiros no desenvolvimento de soluções de arrefecimento por imersão para centros de dados, que podem reduzir significativamente o consumo de energia e estabilizar as temperaturas dos chips. No entanto, a integração destas tecnologias de arrefecimento diretamente nas embalagens dos chips continua a ser um desafio para o futuro.

Em suma, a TSMC está a liderar a evolução para processadores maiores e mais integrados, superando obstáculos significativos de engenharia para alimentar a próxima vaga de inovações em IA e HPC.

Nenhum comentário

Seja o primeiro!